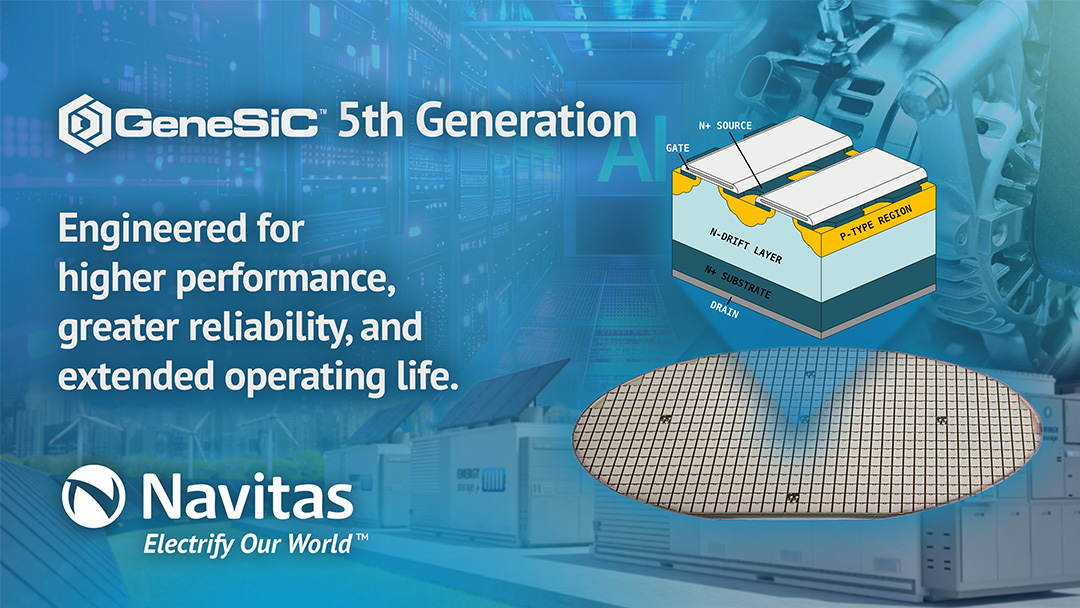

纳微推出第五代碳化硅沟槽辅助平面MOSFET技术

分享

分享

盖世汽车讯 据外媒报道,GaNFast™氮化镓(GaN)和GeneSiC™碳化硅(SiC)功率半导体公司纳微半导体(Navitas Semiconductor)宣布推出其第五代GeneSiC技术平台。该高压(HV)碳化硅沟槽辅助平面(Trench-Assisted Planar,TAP)MOSFET技术较前几代产品实现了显著的技术飞跃,并将提供1200伏MOSFET产品线。它具备领先的性能、稳定性和质量,能够为电动汽车、数据中心和可再生能源系统等高功率应用提供更快、更低温、更可靠的功率转换。

图片来源:纳微半导体

第五代MOSFET平台采用纳微迄今为止最紧凑的TAP架构,结合了平面栅极的坚固性和源区沟槽结构带来的同类最佳性能指标,同时提高了高压电力电子器件的效率和使用寿命可靠性。

与上一代1200伏技术相比,第五代平台的漏源导通电阻×栅漏电荷(RDS,ON×QGD)性能指标(FoM)提升了35%。这一改进显著降低了开关损耗,从而在要求苛刻的功率级中实现更低的运行温度和更高的运行频率。

其高速开关性能的提升得益于QGD/QGS比值约25%的提高。结合稳定的高阈值电压规格(VGS,TH≥3伏),该技术可有效抑制寄生导通干扰,即使在高噪声环境下也能提供稳定可靠的栅极驱动。

第五代技术通过优化RDS(ON)×EOSS特性,显著提高了动态性能,同时还集成了“软体二极管(Soft Body-Diode)”技术,通过最大限度地减少电磁干扰(EMI)并确保高速开关周期中更平稳的换向,进一步增强了系统稳定性。

第五代技术通过了AEC-Plus等级认证,确保了人工智能数据中心、能源和电网基础设施应用的长期稳定性和耐久性。关键可靠性指标包括:

延长压力测试:静态高温高压测试(HTRB、HTGB和HTGB-R)持续时间延长3倍。

高级开关可靠性测试:动态反向偏置(DRB)和动态栅极开关(DGS),以模拟严格的快速开关应用任务剖面。

业界领先的稳定性:在长时间的开关应力测试下,VGS和TH偏移量最低,从而实现稳定的长期效率。

极高的栅极氧化层可靠性:在18伏和175摄氏度的工作VGS下,栅极氧化层失效时间推算超过100万年。

增强的宇宙射线抗干扰能力:极低的故障率(Failure In Time,FIT),确保在高海拔和高正常运行时间环境下的关键任务可靠性。

纳微将在未来几个月内发布基于第五代技术平台的新产品。

欢欢@盖世汽车供应链

欢欢@盖世汽车供应链

悠悠@盖世汽车

悠悠@盖世汽车

豆豆@盖世汽车

豆豆@盖世汽车